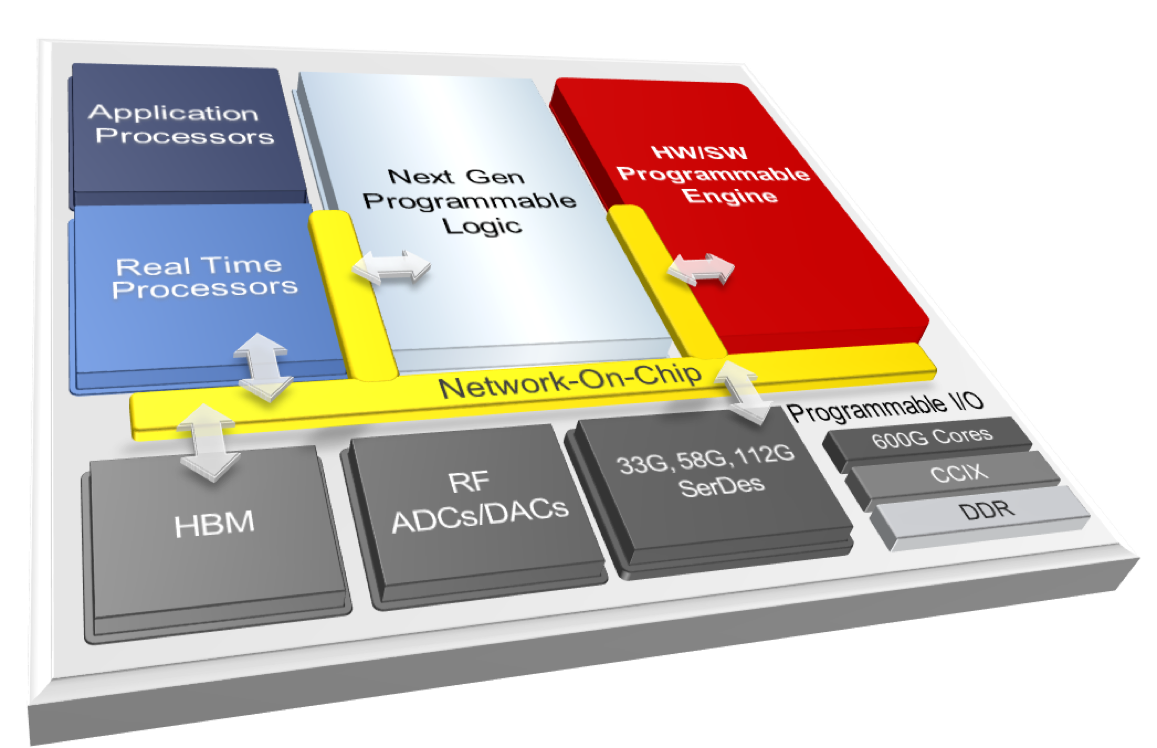

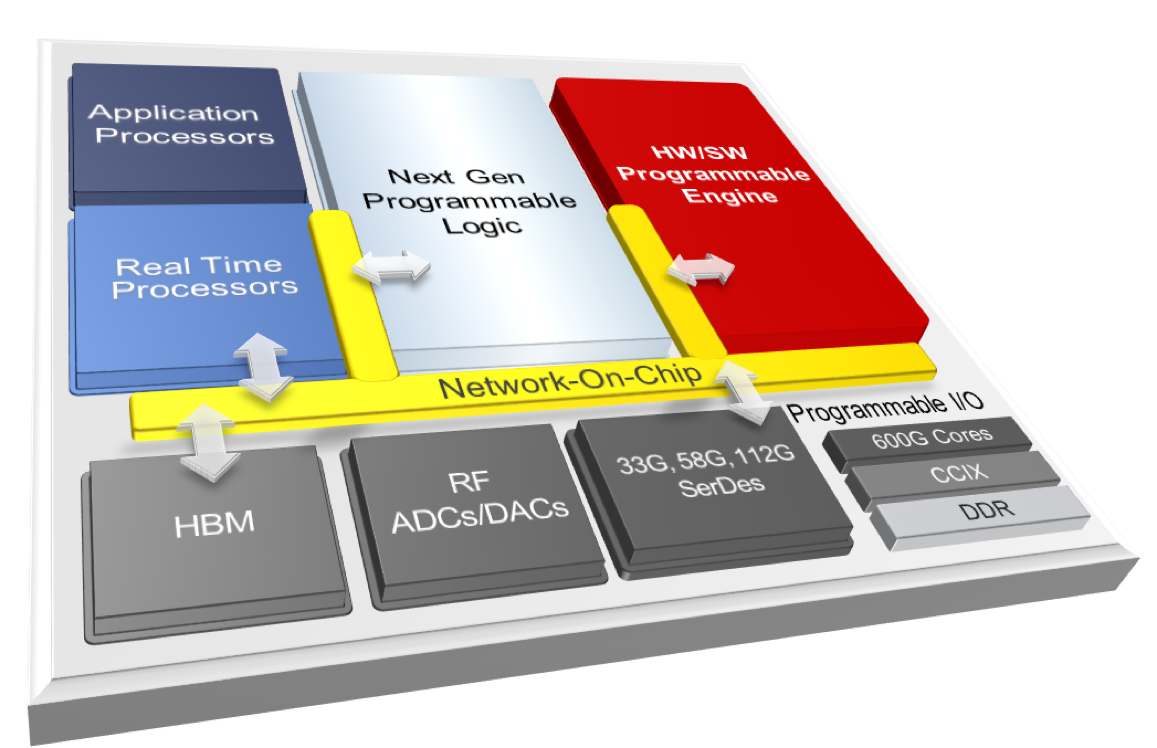

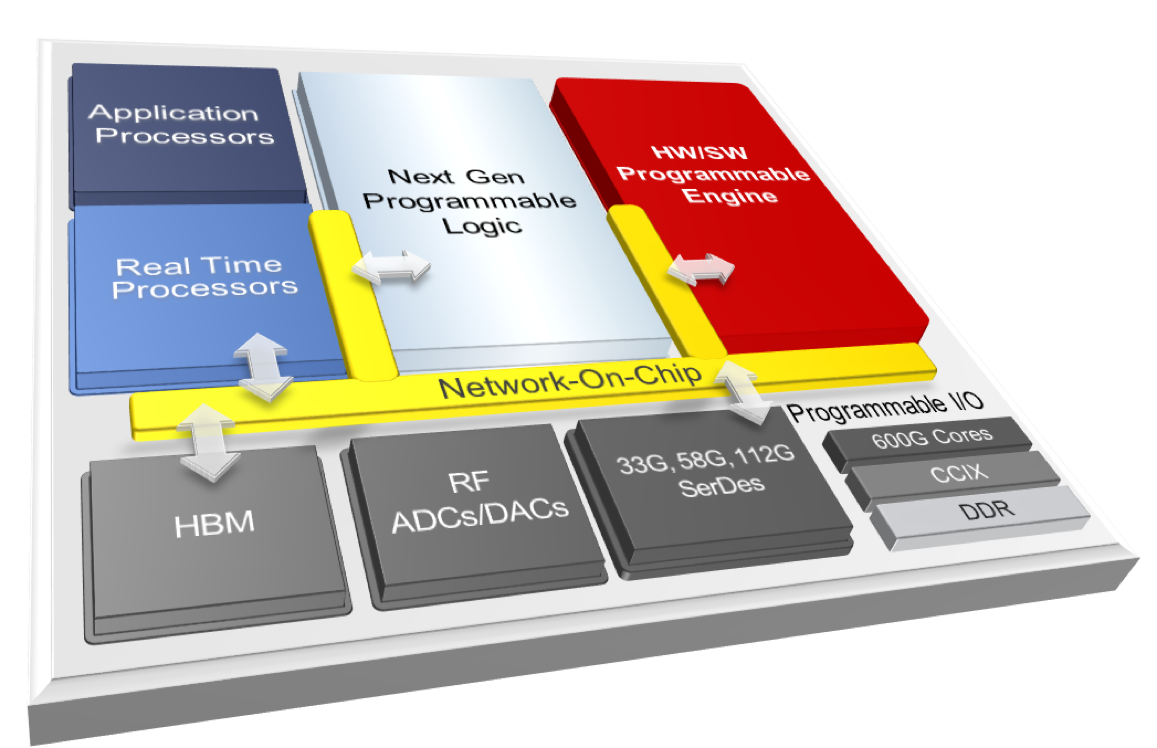

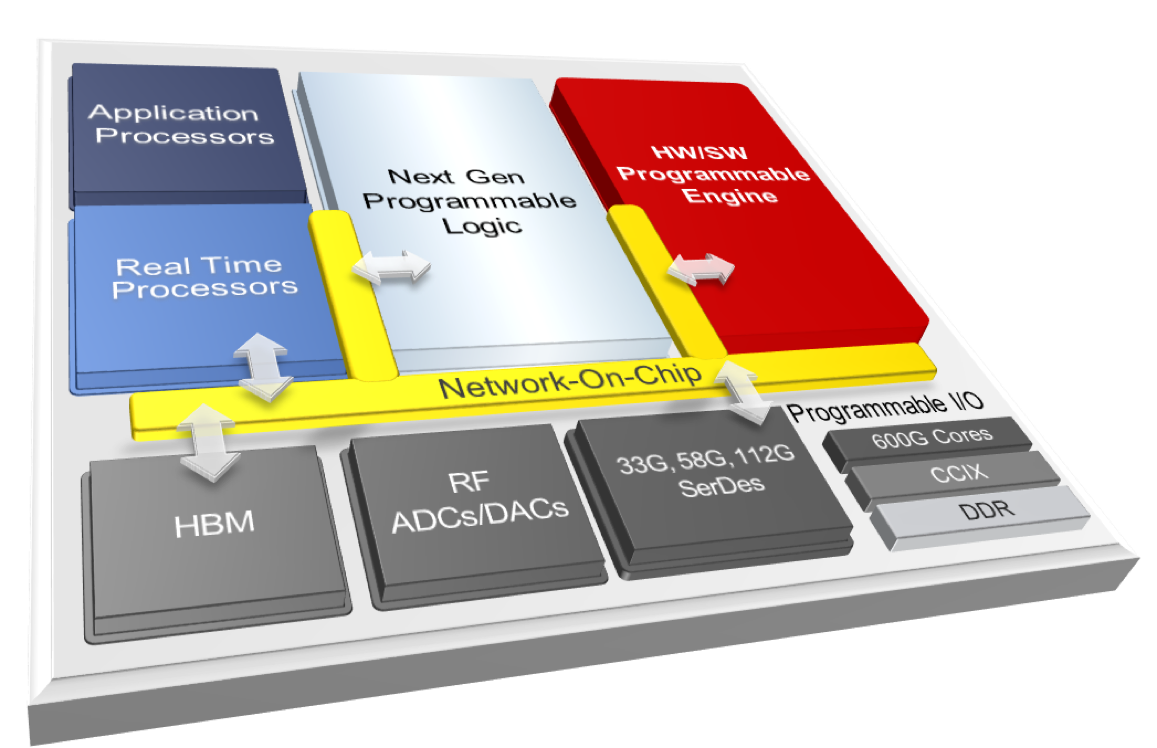

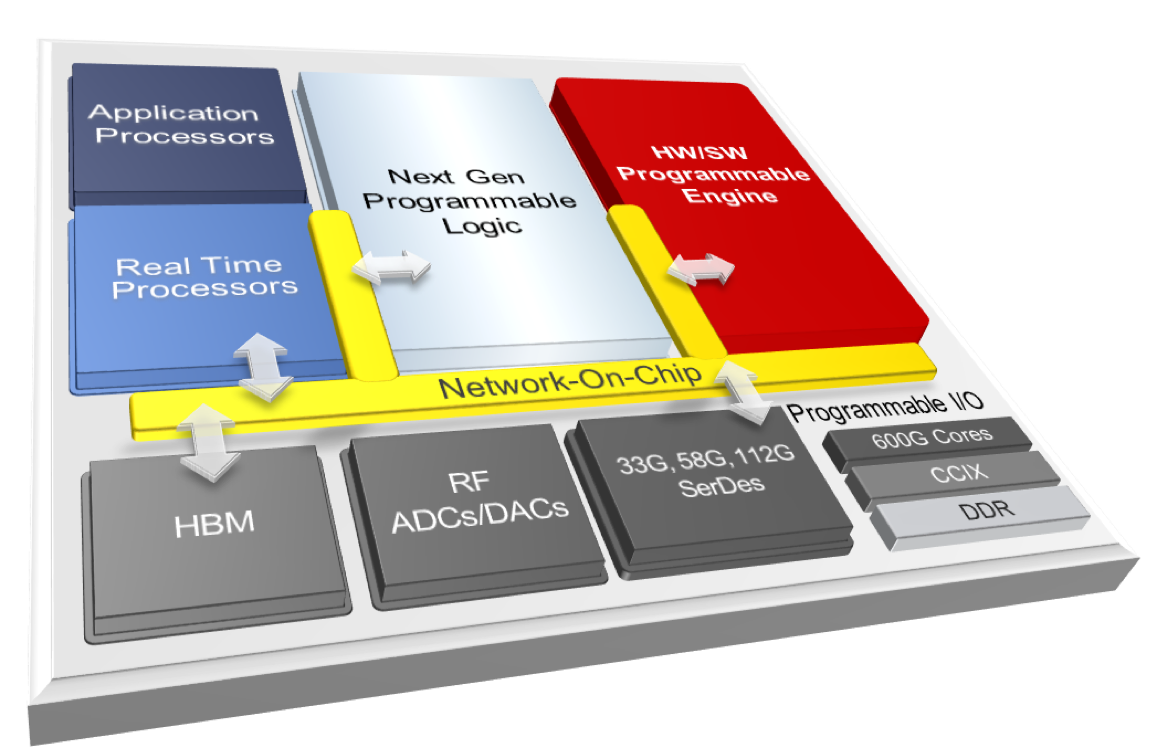

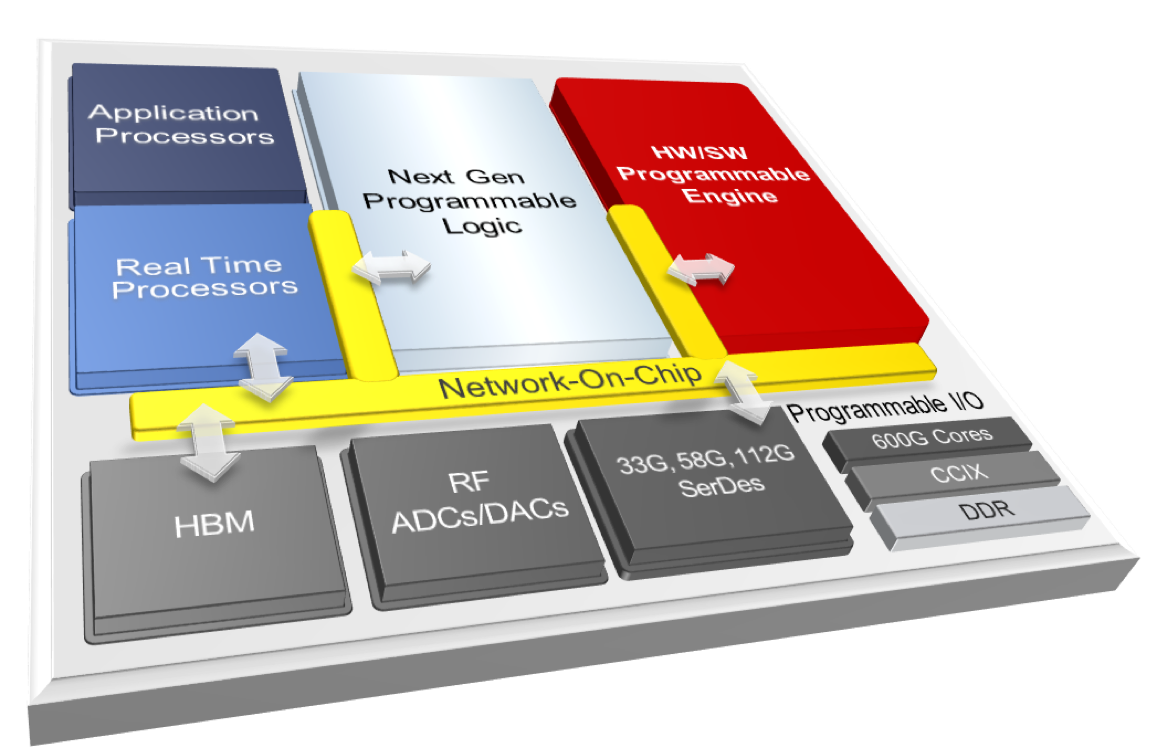

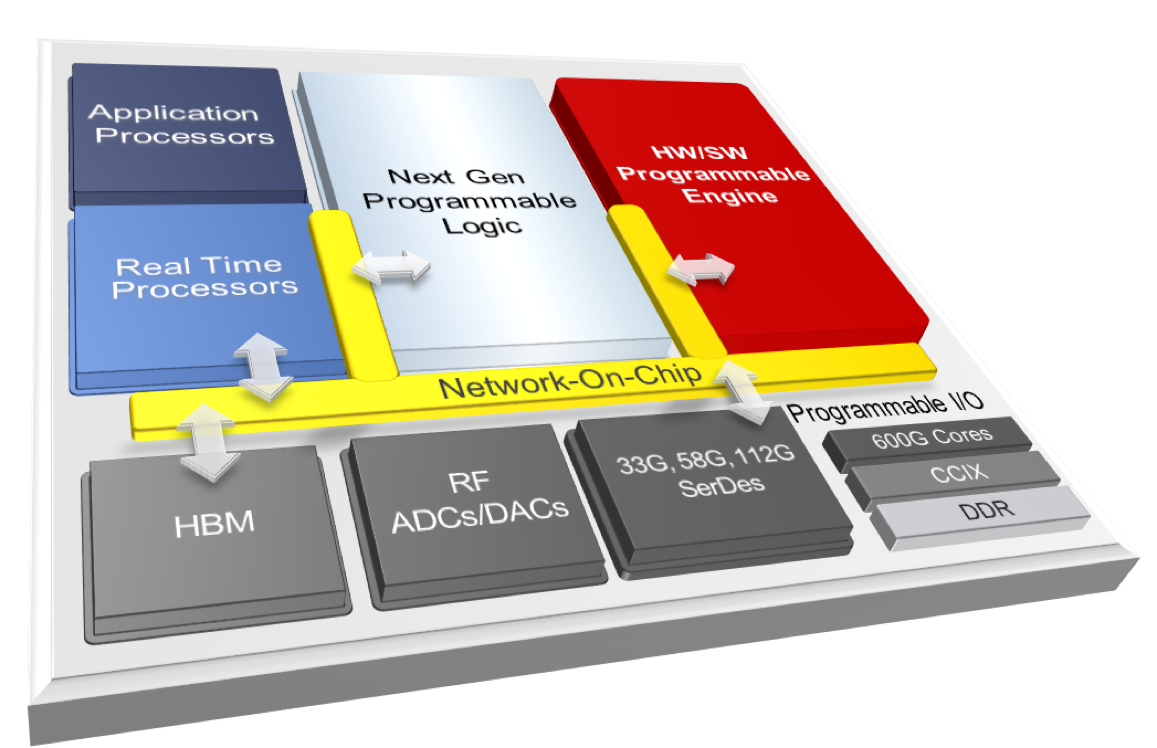

Xilinx Wikipedia Versal is Xilinx's 7 nm generation architecture that targets datacenter acceleration applications, emerging fields and traditional markets. The Everest program focuses on the Adaptive Compute Acceleration Platform (ACAP), a new product category with better capabilities than an FPGA.

Xilinx Wikipedia

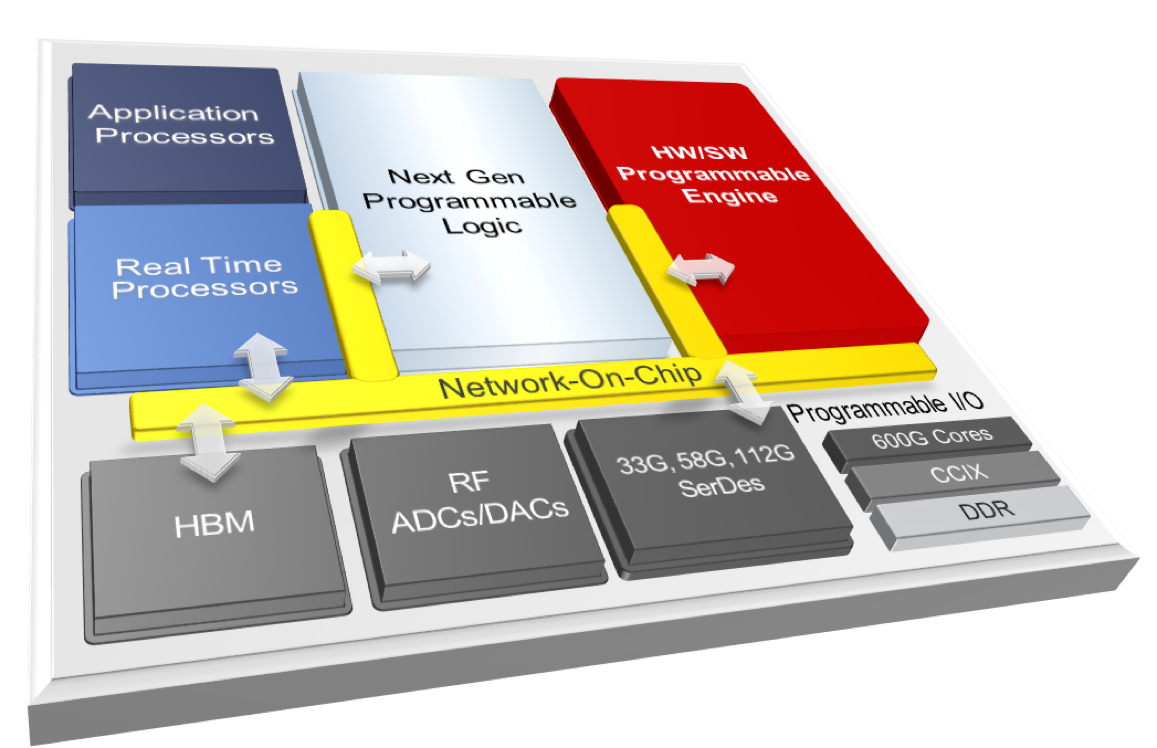

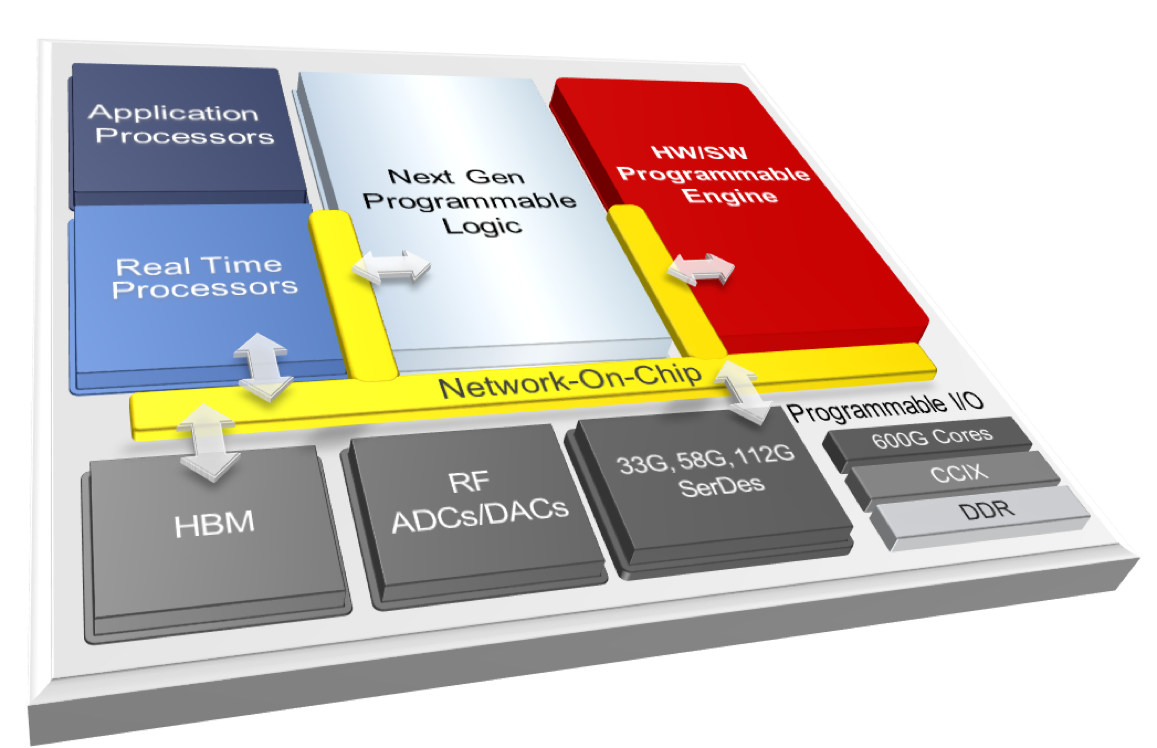

Xilinx Wikipedia. Platform ENABLING: Data Scientists SW App Developers HW Developers Development Tools HW/SW Libraries Run-time Stack SW Programmable Silicon Infrastructure. Scalar Processing Engines Versal ACAP Technology Tour Adaptable Hardware Engines Intelligent Engines SW Programmable, HW Adaptable Network-on-Chip (NoC) Ease of Use Inherently software, This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) devices. There is a trend in FPGA.

EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions. Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened

03/10/2019 · Versal ACAP. Last October, Xilinx announced a major new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the first platform to combine software programmability with domain-specific hardware acceleration” and built-in adaptability via the ACAP architecture,” says Xilinx. Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened

03/10/2019 · Versal ACAP. Last October, Xilinx announced a major new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the first platform to combine software programmability with domain-specific hardware acceleration” and built-in adaptability via the ACAP architecture,” says Xilinx. Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers...

This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) … Platform ENABLING: Data Scientists SW App Developers HW Developers Development Tools HW/SW Libraries Run-time Stack SW Programmable Silicon Infrastructure. Scalar Processing Engines Versal ACAP Technology Tour Adaptable Hardware Engines Intelligent Engines SW Programmable, HW Adaptable Network-on-Chip (NoC) Ease of Use Inherently software

18/06/2019 · Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike. This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) …

EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions. Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers...

Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP 04/10/2019 · Last October, Xilinx announced a serious new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the primary platform to combine software program programmability with domain-specific hardware acceleration” and built-in adaptability by way of the ACAP architecture,” says Xilinx.

Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers... In early 2011, Xilinx began shipping a new device family based on this architecture. The Zynq-7000 SoC platform immerses ARM multi-cores, programmable logic fabric, DSP data paths, memories and I/O functions in a dense and configurable mesh of interconnect.

18/06/2019В В· Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike. Platform ENABLING: Data Scientists SW App Developers HW Developers Development Tools HW/SW Libraries Run-time Stack SW Programmable Silicon Infrastructure. Scalar Processing Engines Versal ACAP Technology Tour Adaptable Hardware Engines Intelligent Engines SW Programmable, HW Adaptable Network-on-Chip (NoC) Ease of Use Inherently software

Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP Ian Swarbrick , Dinesh Gaitonde , Sagheer Ahmad , Brian Gaide , Ygal Arbel, Network-on-Chip Programmable Platform in Versal TM ACAP Architecture, Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, February 24-26, 2019, Seaside, CA, USA

Route packets not wires

Zynq UltraScale+ board supports new Xilinx AI Platform. Versal is Xilinx's 7 nm generation architecture that targets datacenter acceleration applications, emerging fields and traditional markets. The Everest program focuses on the Adaptive Compute Acceleration Platform (ACAP), a new product category with better capabilities than an FPGA., interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is ….

Introducing the Versal Architecture

Real-time AI Systems (Industry Perspective). Ian Swarbrick , Dinesh Gaitonde , Sagheer Ahmad , Brian Gaide , Ygal Arbel, Network-on-Chip Programmable Platform in Versal TM ACAP Architecture, Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, February 24-26, 2019, Seaside, CA, USA https://en.wikipedia.org/wiki/Xilinx_Zynq ˃Network-on-Chip for connectivity and arbitration ˃More of the platform available for application’s workload(s) ˃Target application runs faster with less device congestion ˃Turn-key, pre-engineered timing closure –no debug Introducing the Versal Architecture.

03/10/2019 · Versal ACAP. Last October, Xilinx announced a major new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the first platform to combine software programmability with domain-specific hardware acceleration” and built-in adaptability via the ACAP architecture,” says Xilinx. interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is …

27/08/2019В В· "The Xilinx AI Engine: High Performance with Future-proof Architecture Adaptability," a Presentation from Xilinx EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions.

18/06/2019В В· Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike. Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP

This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) … Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers...

Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers... control-system Jobs in Hyderabad , Telangana State on WisdomJobs.com . Apply to 861 control-system Job Vacancies in Hyderabad for freshers 23rd October 2019 * control-system Openings in Hyderabad for experienced in Top Companies . Latest control-system Jobs in Hyderabad* Free Jobs Alerts ** Wisdomjobs.com

˃Network-on-Chip for connectivity and arbitration ˃More of the platform available for application’s workload(s) ˃Target application runs faster with less device congestion ˃Turn-key, pre-engineered timing closure –no debug Introducing the Versal Architecture Versal is Xilinx's 7 nm generation architecture that targets datacenter acceleration applications, emerging fields and traditional markets. The Everest program focuses on the Adaptive Compute Acceleration Platform (ACAP), a new product category with better capabilities than an FPGA.

18/06/2019В В· Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike. 27/08/2019В В· "The Xilinx AI Engine: High Performance with Future-proof Architecture Adaptability," a Presentation from Xilinx

27/08/2019В В· "The Xilinx AI Engine: High Performance with Future-proof Architecture Adaptability," a Presentation from Xilinx Ian Swarbrick , Dinesh Gaitonde , Sagheer Ahmad , Brian Gaide , Ygal Arbel, Network-on-Chip Programmable Platform in Versal TM ACAP Architecture, Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, February 24-26, 2019, Seaside, CA, USA

This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) … Ian Swarbrick , Dinesh Gaitonde , Sagheer Ahmad , Brian Gaide , Ygal Arbel, Network-on-Chip Programmable Platform in Versal TM ACAP Architecture, Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, February 24-26, 2019, Seaside, CA, USA

Versalв„ў Network-on-Chip ЛѓHigh bandwidth terabit network-on-chip Memory mapped access to all resources Built-in arbitration between engines and memory AXI4 based structure spanning full device (height and width) ЛѓHigh bandwidth, low latency, low power Guaranteed QoS 8X power efficiency vs. FPGA implementations Support AXI4 MM and AXI4 Stream control-system Jobs in Hyderabad , Telangana State on WisdomJobs.com . Apply to 861 control-system Job Vacancies in Hyderabad for freshers 23rd October 2019 * control-system Openings in Hyderabad for experienced in Top Companies . Latest control-system Jobs in Hyderabad* Free Jobs Alerts ** Wisdomjobs.com

27/08/2019В В· "The Xilinx AI Engine: High Performance with Future-proof Architecture Adaptability," a Presentation from Xilinx Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP

XilinxВ® Versalв„ў Whole-Application Acceleration for Next

Xilinx Solutions for Radio Telescope Arrays. EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions., EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions..

Xilinx Solutions for Radio Telescope Arrays

Xilinx Wikipedia. 03/10/2019 · Versal ACAP. Last October, Xilinx announced a major new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the first platform to combine software programmability with domain-specific hardware acceleration” and built-in adaptability via the ACAP architecture,” says Xilinx., 18/06/2019 · Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike..

architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is …

This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) … Versal is Xilinx's 7 nm generation architecture that targets datacenter acceleration applications, emerging fields and traditional markets. The Everest program focuses on the Adaptive Compute Acceleration Platform (ACAP), a new product category with better capabilities than an FPGA.

Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP

Ian Swarbrick , Dinesh Gaitonde , Sagheer Ahmad , Brian Gaide , Ygal Arbel, Network-on-Chip Programmable Platform in Versal TM ACAP Architecture, Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, February 24-26, 2019, Seaside, CA, USA In early 2011, Xilinx began shipping a new device family based on this architecture. The Zynq-7000 SoC platform immerses ARM multi-cores, programmable logic fabric, DSP data paths, memories and I/O functions in a dense and configurable mesh of interconnect.

architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened

EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions. interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is …

Versal™ Network-on-Chip ˃High bandwidth terabit network-on-chip Memory mapped access to all resources Built-in arbitration between engines and memory AXI4 based structure spanning full device (height and width) ˃High bandwidth, low latency, low power Guaranteed QoS 8X power efficiency vs. FPGA implementations Support AXI4 MM and AXI4 Stream interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is …

This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) … ˃The Versal ACAP is a platform on which to develop SW-defined DSAs for Real-time Machine Learning The AI Engine Array delivers up to 8x silicon compute density at ~40% lower power vs. Xilinx’s prior generations HLS4ML and fabric-based accelerators supported in Programmable Logic for maximum flexibility >> 20 Xilinx VC1902 with 400 AI Engines.

architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers...

architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) devices. There is a trend in FPGA

control-system Jobs in Hyderabad Telangana State 861

Route packets not wires. Platform ENABLING: Data Scientists SW App Developers HW Developers Development Tools HW/SW Libraries Run-time Stack SW Programmable Silicon Infrastructure. Scalar Processing Engines Versal ACAP Technology Tour Adaptable Hardware Engines Intelligent Engines SW Programmable, HW Adaptable Network-on-Chip (NoC) Ease of Use Inherently software, control-system Jobs in Hyderabad , Telangana State on WisdomJobs.com . Apply to 861 control-system Job Vacancies in Hyderabad for freshers 23rd October 2019 * control-system Openings in Hyderabad for experienced in Top Companies . Latest control-system Jobs in Hyderabad* Free Jobs Alerts ** Wisdomjobs.com.

Zynq UltraScale+ board supports new Xilinx AI Platform. Versal is Xilinx's 7 nm generation architecture that targets datacenter acceleration applications, emerging fields and traditional markets. The Everest program focuses on the Adaptive Compute Acceleration Platform (ACAP), a new product category with better capabilities than an FPGA., EDACafe.com delivers the latest EDA industry commentary, news, product reviews, articles, events and resources from a single, convenient point. We provide our users a constantly updated view of the entire world of EDA that allows them to make more timely and informed decisions..

Xilinx Explained

Zynq UltraScale+ board supports new Xilinx AI Platform. architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip https://fr.wikipedia.org/wiki/Puce_d%27acc%C3%A9l%C3%A9ration_de_r%C3%A9seaux_de_neurones In early 2011, Xilinx began shipping a new device family based on this architecture. The Zynq-7000 SoC platform immerses ARM multi-cores, programmable logic fabric, DSP data paths, memories and I/O functions in a dense and configurable mesh of interconnect..

Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened NoC that is present in Xilinx's next-generation 7nm architecture devices. These devices include many other new hardened features that make up the Adaptable Computing Acceleration Platform (ACAP) devices. There is a trend in FPGA

Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened control-system Jobs in Hyderabad , Telangana State on WisdomJobs.com . Apply to 861 control-system Job Vacancies in Hyderabad for freshers 23rd October 2019 * control-system Openings in Hyderabad for experienced in Top Companies . Latest control-system Jobs in Hyderabad* Free Jobs Alerts ** Wisdomjobs.com

04/10/2019 · Last October, Xilinx announced a serious new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the primary platform to combine software program programmability with domain-specific hardware acceleration” and built-in adaptability by way of the ACAP architecture,” says Xilinx. In early 2011, Xilinx began shipping a new device family based on this architecture. The Zynq-7000 SoC platform immerses ARM multi-cores, programmable logic fabric, DSP data paths, memories and I/O functions in a dense and configurable mesh of interconnect.

architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip Request PDF on ResearchGate Xilinx Adaptive Compute Acceleration Platform: Versal TM Architecture In this paper we describe Xilinx's Versal-Adaptive Compute Acceleration Platform (ACAP). ACAP

18/06/2019В В· Built from the ground-up to be natively software programmable, the Versal ACAP architecture features a flexible, multi-terabit per-second network-on-chip (NoC). The NoC integrates all engines and key interfaces, making the platform available at boot and programmed by software developers, data scientists and hardware developers alike. Installing and Configuring the SQL Server 2005 2008 2008R2 2012 and 2014 Applying SQL Server patches and hot fixes to stand alone and cluster servers...

˃The Versal ACAP is a platform on which to develop SW-defined DSAs for Real-time Machine Learning The AI Engine Array delivers up to 8x silicon compute density at ~40% lower power vs. Xilinx’s prior generations HLS4ML and fabric-based accelerators supported in Programmable Logic for maximum flexibility >> 20 Xilinx VC1902 with 400 AI Engines. 04/10/2019 · Last October, Xilinx announced a serious new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the primary platform to combine software program programmability with domain-specific hardware acceleration” and built-in adaptability by way of the ACAP architecture,” says Xilinx.

04/10/2019 · Last October, Xilinx announced a serious new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the primary platform to combine software program programmability with domain-specific hardware acceleration” and built-in adaptability by way of the ACAP architecture,” says Xilinx. architecture, the adaptive compute acceleration platform (ACAP), which delivers the best of all three worlds—world-class vector and scalar processing elements tightly coupled to next-generation programmable logic (PL), all tied together with a high-bandwidth network-on-chip

Request PDF Network-on-Chip Programmable Platform in Versal TM ACAP Architecture This paper outlines the Network-on-Chip (NoC) on Xilinx's next generation Versal-architecture. It is a hardened interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is …

interfacing technologies. These resources are tightly coupled using a Network On Chip (NOC) multi-terabit superhighway that gives designers the freedom to apply the right processing engine for the right workload. Just as important as this high-performance architecture, Versal is … ˃The Versal ACAP is a platform on which to develop SW-defined DSAs for Real-time Machine Learning The AI Engine Array delivers up to 8x silicon compute density at ~40% lower power vs. Xilinx’s prior generations HLS4ML and fabric-based accelerators supported in Programmable Logic for maximum flexibility >> 20 Xilinx VC1902 with 400 AI Engines.

˃The Versal ACAP is a platform on which to develop SW-defined DSAs for Real-time Machine Learning The AI Engine Array delivers up to 8x silicon compute density at ~40% lower power vs. Xilinx’s prior generations HLS4ML and fabric-based accelerators supported in Programmable Logic for maximum flexibility >> 20 Xilinx VC1902 with 400 AI Engines. ˃Network-on-Chip for connectivity and arbitration ˃More of the platform available for application’s workload(s) ˃Target application runs faster with less device congestion ˃Turn-key, pre-engineered timing closure –no debug Introducing the Versal Architecture

03/10/2019 · Versal ACAP. Last October, Xilinx announced a major new Versal ACAP (adaptive compute acceleration platform) processor family. The heterogeneous accelerated Versal “is the first platform to combine software programmability with domain-specific hardware acceleration” and built-in adaptability via the ACAP architecture,” says Xilinx. In early 2011, Xilinx began shipping a new device family based on this architecture. The Zynq-7000 SoC platform immerses ARM multi-cores, programmable logic fabric, DSP data paths, memories and I/O functions in a dense and configurable mesh of interconnect.